赛灵思推出用于AI推理的XDNN FPGA架构

2018年08月29日 由 浅浅 发表

61208

0

FPGA可能没有像一些人预期的那样在深度学习训练空间中占据一席之地,但AI推理的低功耗,高频率需求非常适合可重编程硬件的曲线。

然而,现在专注于推理与训练的新体系结构,FPGA必须努力保持领先于定制硬件的工作,这些工作依赖于高级编程工具来抵消一些复杂性。现在判断通用CPU,GPU,FPGA或定制芯片如何吸引最广泛的推理用户群还为时尚早,但现在已经准备就绪的基于云的FPGA以及不断发展的高级FPGA集可用于实验的工具,FPGA在推理中占据了一席之地。

FPGA制造商赛灵思发布了一些关于赛灵思深层神经网络推理设备xDNN的细节,该在Hot Chips上有更多的信息,10月1日将在公司开发者大会上发布详细信息和基准。值得注意的是,就在几年前,神经网络训练处理器是架构展的明星,由于GPU在定制化的ASIC和其他通用硬件上的竞争异常激烈,这场战争蔓延到了推理领域。

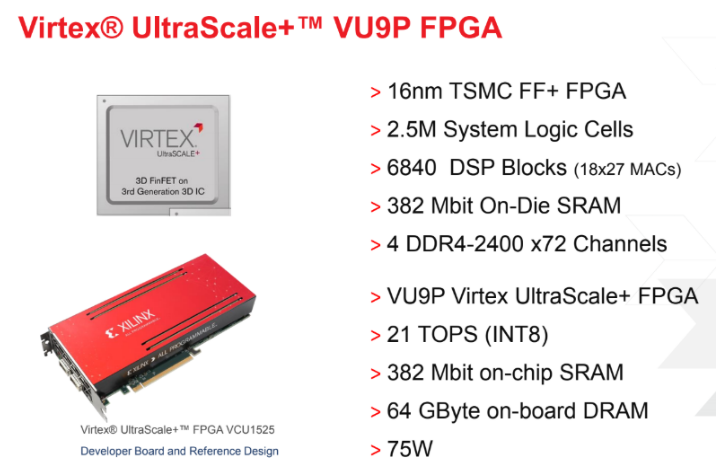

xDNN可配置覆盖处理器将一系列神经网络框架映射到VU9P Virtex UltraScale + FPGA上,提供增强内存,使用自定义应用程序的选项,在亚马逊云上使用F1实例或内部的时候,可以使用编译器和运行时。

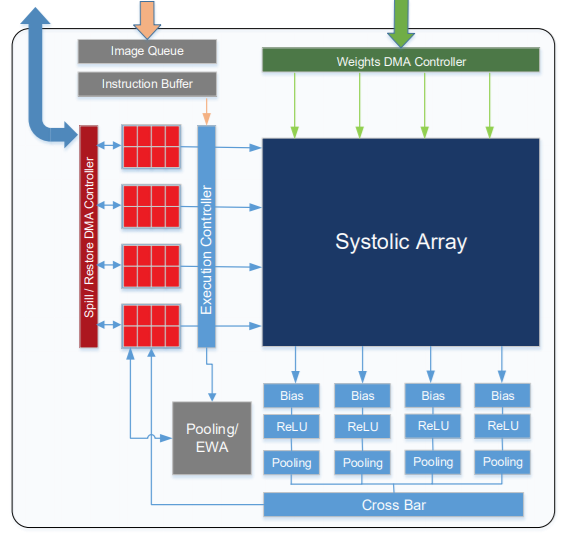

作为赛灵思的数据中心和IP总监,Rahul Nimaiyar上周在Hot Chips告诉我们,FPGA推理故事基于坚实的硬件基础。FPGA是数据并行的,并且支持数据重用以及数据压缩和应对数据稀疏,以及xDNN处理器的2D二维MAC阵列,灵活的高带宽片上存储器访问以及多种方式,数据移动更加高效。xDNN还支持灵活的数据类型(即FP32 / FP16和INT 16/8/4/2等)。

xDNN是一个可配置的覆盖处理器,这意味着它可以映射到FPGA上而无需重新编程。赛灵思还提供了DNN特定指令集(卷积,最大池化等),可以处理任何网络或图像大小,还可以编译和运行新网络。换句话说,它可以与TensorFlow一起使用,而无需重新编程或更改FPGA。

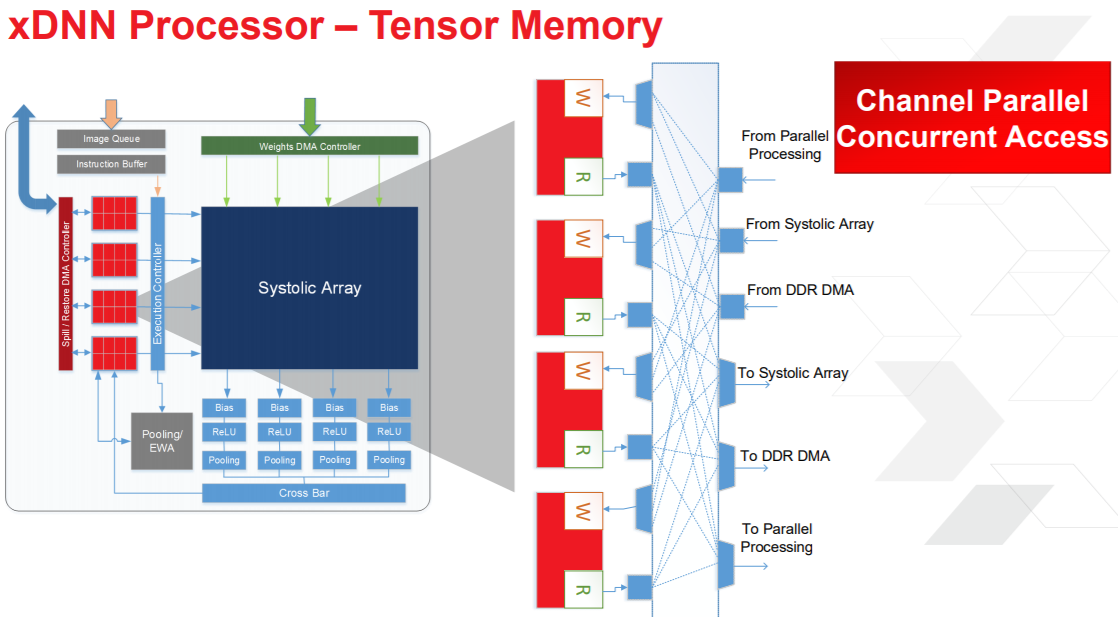

Virtex硬件可以用几种类型的存储器,从位于DSP模块旁边的基本分布式RAM到UltraRAM,高带宽内存和外部DDR4。这允许优化效率或提升性能。

上面是一个通道并行脉动阵列的示意图,显示了分布式加权缓冲区。处理元件与权重一起映射到DSP块上,权重保存在处理旁边的快速但低容量的分布式RAM中。换句话说,这些分布式RAM是权重缓存。

xDNN的“Tensor Memory”位于脉动阵列的旁边,并保持输入和输出特征映射。这也是通道并行,因此该阵列中的每个行都与一行内存相关联。这意味着xDNN可以进行多任务处理,在阵列上进行计算,同时还可以根据需要引入新的网络层。

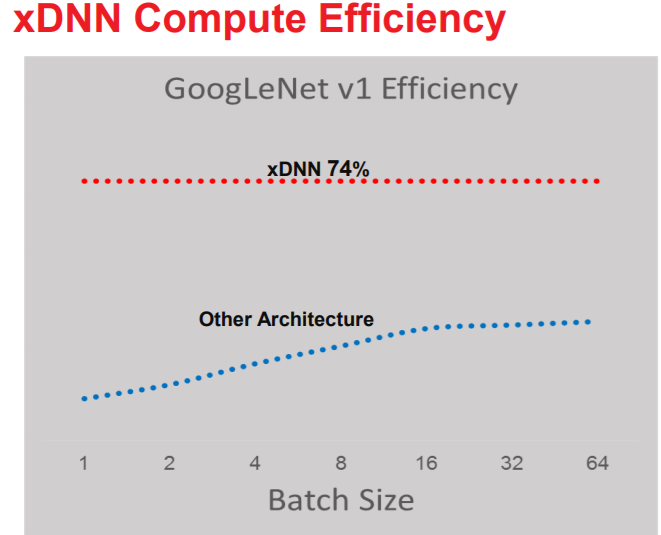

与其他推理芯片一样,有足够多的片上存储器可以有效地压缩以保持芯片上的激活,这对于提高效率是一项艰难的平衡行为,但正如下面的基准测试所示,赛灵思的配置似乎有效。

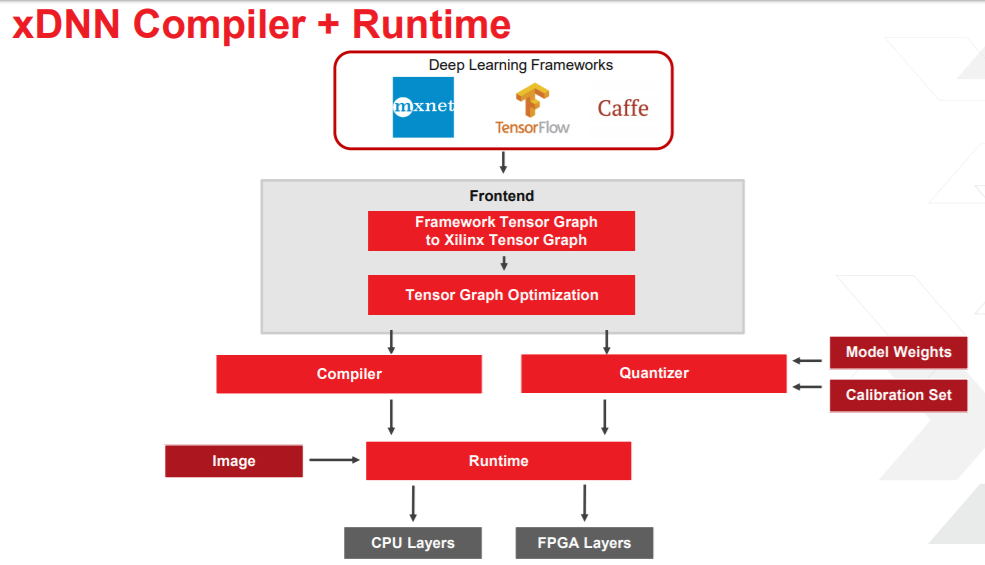

除了硬件之外,从易用性角度来看真正的关键,特别是对于那些尝试使用F1进行深度学习以及更新到FPGA编程更精细点的人来说,就是编译器和运行时。

有关赛灵思为用户开发的ML工具套件的更多信息,但实质上,这是一个允许连接到框架的API,并且可以更容易地在Tensorflow中获得经过训练的模型和权重,例如,将其转换为一个赛灵思图,在它到达编译器之前通过一些优化,生成所有必要的指令集以在xDNN上运行该网络。赛灵思还有一个量化器,因此可以将经过训练的权重提供给具有一些校准集的权重,以找到范围并快速获得量化权重。

“简而言之,这是在进行大量的图形分区。有很多预处理和后处理,我们使用子图让我们在主机CPU的不同代码甚至部分代码上运行图形的不同部分,”Nimaiyar解释说。赛灵思已经抽象出了导致有效推理的其他元素,包括操作的融合(一旦访问激活,它们可以作为管道运算符执行而不返回Tensor Memory),指令级并行性和自动层内平铺当特征映射大小超过片上存储器时,这意味着xDNN可以处理任何特征映射大小。

下面的稀疏基准是赛灵思自己对赛灵思开发者论坛上发生的体系结构和产品的展示,但到目前为止,60-80%的跨框架效率数据表现足以让人期待。

欢迎关注ATYUN官方公众号

商务合作及内容投稿请联系邮箱:bd@atyun.com

热门企业

热门职位

写评论取消

回复取消